Lvds что это в ноутбуке

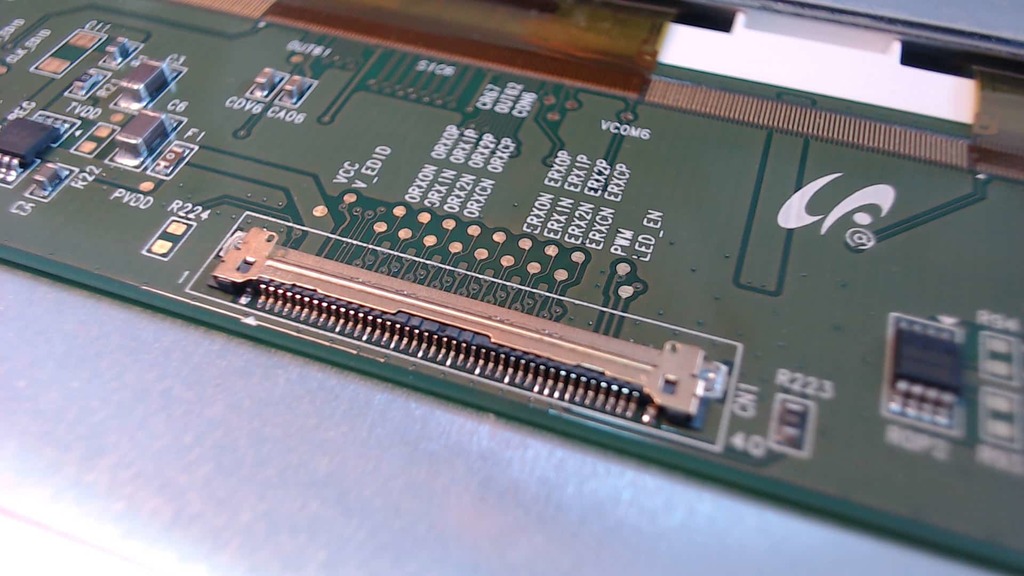

Что такое LVDS (30 пиновый широкий и 40 пиновый разъем матриц)

Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компанией Texas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин.

Отличия от несимметричной передачи сигналов

При дифференциальной передаче для передачи одного сигнала используется дифференциальная пара (сигналов); это означает, что передающая сторона подаёт на проводники пары различные уровни напряжения, которые сравниваются на приёмной стороне: для декодирования информации используется разница напряжений на проводниках пары. Передатчик направляет небольшой ток (порядка 3,5 мА) в один из сигнальных проводников, в зависимости от того, какой логический уровень надо передать. На приёмной стороне ток проходит через резистор сопротивлением 100—120 Ом (равным волновому сопротивлению кабеля для уменьшения отраженного сигнала) и возвращается к отправителю сигнала по другому проводнику, образуя таким образом замкнутую электрическую цепь. В соответствии с законом Ома напряжение на резисторе будет составлять около 350 мВ. Принимающая сторона определяет полярность этого напряжения для того, чтобы определить логический уровень. Такой тип передачи называется токовая петля.

Небольшая амплитуда сигнала LVDS, а также высокая электромагнитная связь проводов дифференциальной пары друг с другом позволяют уменьшить излучаемые вовне помехи и рассеиваемую мощность.

LVDS — не единственная используемая дифференциальная система. Но она остается единственной, сочетающей в себе высокие скорости и небольшое рассеивание энергии.

LVDS используется в таких компьютерных шинах как HyperTransport, FireWire, USB 3.0, PCI Express, DVI, Serial ATA, SAS и RapidIO, а так же интерфейс LVDS на текущий момент времени является самым распространенным интерфейсом из всех используемых в мониторах настольного типа и в матрицах для ноутбуков. По сравнению с TMDS, интерфейсом LVDS обеспечивается более высокая пропускная способность, что и привело к тому, что LVDS, фактически, стал стандартом внешнего интерфейса для современной LCD-панели.

LVDS способен передавать до 24 битов информации за один пиксельный такт, что соответствует режиму True Color (16.7 млн. цветов). При этом исходный поток параллельных данных (18 бит или 24 бита) конвертируется в 4 дифференциальные пары последовательных сигналов с умножением исходной частоты в семь раз. Тактовая частота передается по отдельной дифференциальной паре. Уровни рабочих сигналов составляют 345 мВ, выходной ток передатчика имеет величину от 2.47 до 4.54 мА, а стандартная нагрузка равна 100 Ом. Данный интерфейс позволяет обеспечить надежную передачу данных с полосой пропускания свыше 455 МГц без искажений на расстояние до нескольких метров.

Трансмиттер LVDS состоит из четырех 7-разрядных сдвиговых регистров, умножителя частоты и выходных дифференциальных усилителей

Достаточно часто в литературе, в документации и на схемах можно встретить и несколько другое обозначение сигналов интерфейса LVDS. Так, в частности, широко применяется такое обозначение, как RX0+/-, RX1+/-, RX2+/-, RX3+/- и RXC+/-.

Входной сигнал CLK представляет собой сигнал пиксельной частоты (Pixel Clock) и он определяет частоту формирования сигналов R/G/B на входе трансмиттера. Умножитель частоты умножает частоту CLK в 7 раз. Полученный тактовый сигнал (7xCLK) используется для тактирования сдвиговых регистров, а также передается по дифференциальным линиям CLKP/CLKM.

7-разрядный параллельный код загружается в сдвиговые регистры трансмиттера по стробирующему сигналу, вырабатываемому внутренней управляющей логикой трансмиттера. После загрузки начинается поочередное «выталкивание» битов на соответствующую дифференциальную линию, и этот процесс тактируется сигналом 7xCLK.

Таким образом, на каждой из четырех дифференциальных линий данных (Y0P/YOM, Y1P/Y1M, Y2P/Y2M, Y3P/Y3M ) формируется 7-разрядный последовательный код, передаваемый синхронно с тактовыми сигналами на линии CLKP/CLKM.

Обратное преобразование последовательного кода в параллельный осуществляется ресивером, входящим в состав LCD-панели, а поэтому вполне естественно, что ресивер, фактически, является зеркальным отражением трансмиттера.

Интерфейс LVDS используется для передачи как 18-разрябного цветового кода (3 цвета по 6 бит на каждый), так и 24-разрядного цвета (3 базовых цвета по 8 бит). Но в отличие от интерфейса TMDS, здесь каждому цвету не выделяется отдельная дифференциальная пара, т.е. каждый дифференциальный канал LVDS предназначен для передачи отдельных битов разных цветов. Кроме сигналов цвета, на LCD-панель должны передаваться еще:

— сигнал строчной синхронизации (HSYNC);

— сигнал кадровой синхронизации (VSYNC);

— сигнал разрешения данных (DE).

Эти управляющие сигналы также передаются по дифференциальным каналам, предназначенным для передачи данных, т.е. по линиям YnP/YnM. Таким образом, существует два варианта формата данных, передаваемых на LCD-матрицу.

Первый вариант соответствует 18-разрядному цветовому коду, и при этом на вход трансмиттера подается 21 разряд данных. Второй вариант – это 24-разрядный цветовой код, при котором на входе трансмиттера должно быть 27 бит данных.

Итак, стандартный вариант распределения входных сигналов трансмиттера между его сдвиговыми регистрами представлен на рис

В принципе, интерфейс LVDS может использоваться для передачи любых цифровых данных, о чем говорит широкое применение LVDS в телекоммуникационной отрасли. Однако, все-таки, наибольшее распространение он получил именно как дисплейный интерфейс. Для увеличения пропускной способности этого интерфейса, компания разработчик (National Semiconductor) расширила интерфейс LVDS и удвоила количество дифференциальных пар, используемых для передачи данных, т.е. теперь их стало восемь

Это расширение получило название LDI – LVDS Display Interface. Кроме того, в спецификации LDI улучшен баланс линий по постоянному току за счет введения избыточного кодирования, а стробирование производится каждым фронтом такового сигнала (что позволяет вдвое повысить объем передаваемых данных без увеличения тактовой частоты). LDI поддерживает скорость передачи данных до 112 МГц. В документации данная спецификация встречается также и под наименованием OpenLDITM, а в массах специалистов отклик в душе нашел термин «двухканальный LVDS».

Использование одноканального или двухканального LVDS определяется такими характеристиками LCD-панели и монитора, как:

— частота кадровой развертки, т.е. определяется режимом работы.

На сегодняшний день в подавляющей массе 1-канальный LVDS используется в матрицах с разрешением до 1366х768, а начиная с 1600х900 и выше используется 2-х канальный LVDS.

Технология диагностики и ремонта LVDS интерфейса матрицы в ноутбуке.

Автор: STRIDER · Опубликовано 26.06.2018 · Обновлено 17.03.2021

Введение.

Привет! Достаточно часто приходят на ремонт ноутбуки с проблемами вывода изображения на дисплей. Естественно нельзя списать все поломки связанные с выводом изображения исключительно на LVDS или EDP интерфейс. Но разобравшись и поняв принцип работы этого интерфейса, проверив его работу путем несложных измерений. Можно значительно упростить общую диагностику и снизить время, а также стоимость ремонта, исключив ошибочную покупку деталей. Для начала разберемся с теорией, что это вообще за интерфейс, кто придумал, как работает и в чем разница с более новым EDP интерфейсом.

Теория.

Low-voltage differential signaling или LVDS — низковольтная дифференциальная передача сигналов изобретенная и продвигаемая компанией Texas Instruments в 1994 году как дешевый способ передачи данных с использованием двух медных проводников обвитых друг о друга и позднее названых как «витая пара». Стандартизацию как TIA/EIA-644-A данный способ передачи обрел только 2001 году в связи с отсутствием на тот момент потребности в столь высоких скоростях.

Что значит дифференциальная? Дифференциальная передача означает, что сигнал идет не в виде положительного напряжения относительно земли, а относительно инверсии самого себя на соседнем проводнике. Разница между проводниками пары и есть сигнал. Такой способ передачи показал наибольшую помехоустойчивость на больших скоростях передачи данных. Причем максимальное синфазное напряжение обычно 1.3V, что позволяет использовать LVDS во многих интегральных микросхемах, печатных платах, шлейфах с низким рабочим напряжением.

Дифференциальная передача сигнала используется в SCSI, Ethernet, PCI Express, HDMI, Display Port и даже в USB. Когда скорости одной пары недостаточно, возможно использование нескольких пар, этот принцип используется в PCI Express 1x — 16x. Где ширина шины (количество пар) диктует возможную скорость передачи.

Зная все это, не совсем корректно называть LVDS исключительно дисплейным интерфейсом. Это всего лишь метод передачи сигнала до дисплея используя гибкий провод или шлейф. Поэтому разъемы, шлейфы, матрицы различны по используемым типам подключения. Каждый производитель посчитал необходимым разработать свой тип сопряжения системной платы и дисплея. И что мы имеем — многообразие различных дисплеев, шлейфов, разъемов не подходящих друг к другу, но использующих один принцип передачи сигнала. Блин ребята, просто договоритесь…

Так и случилось, в декабре 2008 был доработан и принят стандарт Embedded DisplayPort (eDP) версии 1.0, он был предназначен для использования внутри устройств, например для сопряжения панели дисплея и системной платы ноутбука. Этот стандарт по прежнему использовал дифференциальную передачу, но по другому протоколу и с большей скоростью. Что позволило сократить количество «витых пар». Внедрены энергосберегающие функции и поддержка плавного изменения частоты развертки, режим Self-Refresh (PSR) и многое другое. Но принцип работы остался тем же, а значит диагностика и ремонт классических панелей и панелей с EDP интерфейсом ни чем особенным не отличается. Разве что, становится проще, ввиду меньшего количества пар и контактов на разъемах.

Диагностика и ремонт LVDS интерфейса матрицы ноутбука, на практике.

Питающие напряжения.

Разобравшись с принципом работы шины данных LVDS, EDP и их отличием, далее расскажу об основных питающих напряжениях на примере матрицы AUO B156XW02.

Наиболее часто в ноутбуках для обеспечения работы дисплея используется условно 3 типа питающего напряжения:

Управляющие сигналы.

К управляющим сигналам можно отнести:

Сигнал включения подсветки (VLED_EN) представляет собой один контакт появление на котором напряжения, обычно 3.3V является логической единицей, что означает — подсветку включить. Если на этом контакте будет отсутствовать напряжение, подсветка матрицы не будет работать даже если подается основное напряжение на питание подсветки (VLED).

Яркость подсветки управляется шим сигналом (VPWM_EN). Уровень его напряжения составляет диапазон от 2.1V до 5.5V. А управление яркостью подсветки осуществляется изменением скважности импульсного сигнала. Отсутствие данного сигнала приводит к отключению подсветки.

Последовательность запуска.

Измерения.

Используя данные диаграммы представленной выше, можно понять последовательность запуска матрицы. Но стоит уточнить один момент, отсутствие напряжения VEDID и чтения микросхемы EDID приводит к отсутствию всех напряжений, и сигналов. Так как, системная плата не считала прошивку панели или матрицы. Исключением может быть напряжение VLED, для работы подсветки дисплея.

Если напряжение VEDID присутствует, микросхема EDID читается (обмен на CLK_EDID и DAT_EDID) а напряжение VDD отсутствует. Это свидетельствует о неверной микропрограмме записанной в матрице (EDID) или неисправной системной плате ноутбука, например узел формирования VDD.

В случае отсутствия чтения EDID. При наличии напряжения VEDID и отсутствии обрывов CLK_EDID и DAT_EDID. Скорее всего виновником поломки является видеопроцессор или видеочип на системной плате ноутбука, реже конвертер видеосигнала EDP-LVDS и другие микросхемы отвечающие за вывод видеосигнала. Все зависит от конкретной реализации системной платы.

Естественно если какое-то напряжение отсутствует или занижено, необходимо проверить соответствующие выводы на предмет короткого замыкания и обрывов. Я обычно ставлю мультиметр на измерение сопротивления и проверяю относительно «земли». Что касается проверки линий данных EDID и LVDS, их по возможности смотрят осциллографом на предмет «активности» (пульсаций). За неимением осциллографа можно измерить сопротивление и напряжение относительно «земли». На линиях данных EDID сопротивление не должно быть ниже 100 kOhm, а напряжение приблизительно 3.3V. LVDS — напряжение

1.2-1.3V и сопротивление относительно земли не менее 1 mOhm. Встречаются отклонения, но понятно, что скажем сопротивление в 200 Ohm на линиях данных недопустимо, это свидетельствует о поломке.

При проверке линий LVDS, все пары обычно имеют одинаковые показатели по сопротивлению и напряжению сигнала, так как терминируются от одного источника. В случае если одна из пар пробита «на землю» мы получим «квадрат Малевича» или артефакты на изображении (если повезет, например, картинку через пиксель). Чаще видеосигнал просто блокируется.

Помимо поломок связанных с напряжениями и сигналами, встречаются обрывы GND (Ground — «земли или общей массы, как вам удобнее») или высокое сопротивление относительно GND системной платы. Проверяется это с подключенными компонентами (дисплей, шлейф, системная плата). Мультиметром, в режиме измерения сопротивления одним щупом встаем на GND платы, другим на GND матрицы. Должно быть не более 100 Ohm, так же пробуем во время измерения сгибать шлейфик в местах изгиба и смотреть показания прибора.

И всегда, в диагностике и ремонте необходимо отталкиваться от особенностей реализации схемы системной платы и дисплея, по возможности разумеется.

Конвертеры и переключатели видеосигнала.

Конкуренция, продвижение более новых компонентов, энергосберегающих технологий толкает разработчиков компонентов и системных плат к использованию различных конвертеров, и переключателей видеосигнала. С переключателями вроде все более или менее понятно, если используется 2 видеопроцессора Intel и NVIDIA например, микросхема берет на себя роль переключателя и в нужный момент (при запуске игры) подключает матрицу к высокопроизводительному видеочипу. При переходе на питание с батареи — наоборот. Если на системной плате установлен переключатель, источником управляющих сигналов чаще всего являются оба видеопроцессора и все управляющие сигналы запараллелены.

А вот, конвертер это своего рода активный переходник видеосигнала в корпусе маленькой микросхемы. Вы спросите, зачем? Затем, что производители вынуждены экономить, ставя более старые комплектующие к новым. Матрицу старого образца к современному видеопроцессору работающему только с EDP сигналом. В таких случаях все сигналы необходимо измерять «до» и «после» конвертера. Конвертер в данном случае является источником видеосигнала для матрицы, чтение EDID и управление подсветкой идет из него. А для системной платы, конвертер это — матрица с EDP интерфейсом! В случае поломки и ремонта, получается, двойная работа!

Заключение.

В заключение из всего рассказанного выше, хочется напомнить, что данный материал носит ознакомительный характер и совсем не руководство к действиям. Думаю, эта статья поможет интересующимся и остановит от нежелательных действий безрассудно поверивших в свои силы. Расскажет об общих объемах работ и знаний, необходимых для выполнения ремонта ноутбуков с поломками связанными с выводом изображения.

Ставьте лайки, делайте репосты, подписывайтесь на мою группу вконтакте для получения актуальных постов. Спасибо за уделенное моей статье время, очень надеюсь что был полезен! Всем счастья!

Разбор работы LVDS портов и DMA на отечественном DSP 1967ВН028

В продолжение моих заметок, посвященных разбору функционала процессора от фирмы Миландр 1967ВН28, рассмотрим способы общения с внешними устройствами. В данном процессоре есть возможности общения по следующим информационным каналам. Порты LINK (LVDS) и также имеется параллельный интерфейс, предназначенный для работы с внешней памятью. В данной заметке разберем работу с интерфейсом LINK. Этот интерфейс на отладочной плате выведен на разъемы DVI и процессор имеет всего 4 таких приемопередающих линий. Стоит отметить что этот интерфейс поддерживает одновременный прием и передачу (полный дуплекс). Чтобы эффективно работать с транспортировкой массива данных задействуем каналы DMA. Из одного канала DMA будем грузить данные в передающую линию интерфейса LINK и для первого опыта соединим передающий канал одного из LINKов с его же принимающей стороной, где уже другим каналом DMA организуем прием. Разъем DVI для работы с определенным LINK портом при определенной разрядности передачи выбирается исходя из представленных в паспорте отладочной платы таблиц 8 и 9. Таблички приведены ниже.

Стоит отметить что при некоторых вариантах соединения доступен только 1-битный формат приема/передачи, это связано с тем что не на все разъемы подведено по 4 линии данных.

Теперь перейдем ближе к делу, для начала стоит обратить внимание на конфигурационные порты. В спецификации на микросхему написано что за управлением приемником отвечает регистр LRCTLx, а для передатчика аналогичные функции выполняет регистр LTCTLx ниже приведено их описание.

Оба регистра не могут изменяться в процессе обмена. Запись в оба этих регистра возможна только при сброшенном нулевом разряде.

Так же необходимо сконфигурировать порт внешними сигналами.

На имеющейся у меня отладочной плате эти параметры устанавливаются движковыми переключателями SA14 и SA15. Я выставил TIMR0E в единицу, остальное по идее никак в данной ситуации не интересует.

Пойдем далее, было бы неплохо определиться с выбором канала LINK и каналов DMA. К сожалению, выбрать, бросив монетку у нас не получится ибо в зависимости от выбора LINKа мы можем либо иметь возможность передавать и в формате 4 бит и 1 бит, или только в формате 1го бита.

Далее DMA, в этом процессоре DMA работает не так как например в Cortex, где мы просто указываем «откуда взять и куда положить», а потом добавляем управляющее слово которое пускает процесс. Здесь управляющая структура DMA отдельно задается на приём и на передачу. Управляющей структурой для DMA являются регистры блока управления передачей TCB.

Как пишут в документации, каждый TCB (он же DCx) регистр имеет длину 128 бит и разделен на четыре 32-битных

— регистр индекса (DI);

— регистр X количества и приращения (DX);

— регистр Y количества и приращения (DY);

— регистр управления и указателя цепочки (DP);

Эти четыре регистра образуют 128 разрядный регистр TCB, в который можно загрузить настройки как выровненное счетверенное слово из внутренней памяти посредством цепочки (о том как работает цепочка будет сказано ниже) или с помощью ядра. Для инициирования нового обмена, после завершения текущего, программа должна записать новые параметры в регистры TCB.

Теперь перейдем к выбору LINK и каналов DMA. Все в той же спецификации на микросхему есть полезная табличка.

Так как цифра два – хорошая цифра, то решено выбрать второй LINK. Сразу по табличке видим, что для его передатчика используется канал DMA 6, а для его приемника применяется канал 10. Так же по табличкам 8 и 9 видим что нам подходят разъемы XS4, XS5.

Теперь подробнее про управляющие регистры DMA:

Регистр DI

Данный 32-разрядный регистр содержит начальный адрес блока данных и используется для прямого доступа к памяти. Он может указывать на адрес внешней памяти или внутренней памяти.

Регистр DX

Этот 32-разрядный регистр имеет два поля:

DXM – младшие биты (с 0-го по 15-й или с 0-го по 21-й) хранят значение модификатора адреса (DX_MODIFY), которое используется для изменения адреса после каждой транзакции;

DXC – старшие биты (с 16-го по 31-й или с 22-го по 31-й) хранят значение количества слов (DX_COUNT) в блоке данных, который необходимо передать. Например, если необходимо передать 16 слов данных, непрерывно размещенных в памяти, порциями по 4 слова в каждой передаче, то параметр DXC будет равен 16, а значение DXM будет равно 4. Длина операнда (порции данных) в регистре DP устанавливается равной счетверенному слову.

Существуют ограничения, которые следует принимать во внимание при программировании TCB:

— указатель DI должен содержать адрес, выровненный на границе операнда, определяемого в регистре DP;

— Значение DXM должно быть кратно размеру операнда;

— Значение DXC должно быть кратным длине операнда.

Выбор длины полей модификатора и количества определяется типом обмена, задаваемым полем TY в регистре DP.

Регистр DY – применяется при реализации двумерной передачи но он нам сейчас не понадобится, потому опустим.

Регистр DP – Это настроечный регистр задающий режим работы передатчика\приемника канала. На табличке ниже описание его разрядов.

Теперь о цепочке, как говорилось выше у регистров ТСВ есть вариант загрузки значения от ядра или из внутренней памяти посредством цепочки. В режиме цепочки при разрешении последующей передачи, процессор автоматически перезагружает ТСВ и выполняет следующее задание. Как видно из таблички мы можем работать в режиме однократной передачи установив бит CHEN в ноль. В этом режиме DMA выполнит прием или передачу блока данных в соответствии с настройками регистров DI и DX. В случае если разрешено прерывание сгенерирует прерывание по завершению работы и остановится.

Если же есть необходимость передать не один блок данных, или принимать непрерывный поток данных, то стоит разрешить загрузку следующей цепочки настроек для TCB. Это реализуется установлением бита CHEN в единицу, также необходимо записать в первые 18 битов регистра DP указатель на область памяти в которой хранятся настройки для следующей цепочки. При таком раскладе по завершению работы канал DMA будет сразу получать новые настройки и продолжать работу.

Теперь, когда все, казалось бы, уже выяснено приведу получившийся у меня код, он выполняет однократную передачу пакета данных своему приемнику. Отдельно отмечу, что link работает только с квадрословами, поэтому для DMA других вариантов настроек при работе с link быть не может.

Применим все это дело теперь на практике. Сначала реализуем однократную передачу блока данных от процессора к самому себе.

Сначала выделим память под буфер приема и буфер передачи

Далее выключим все LVDS порты и каналы DMA

Теперь включаем Link передатчика, а затем выдержав драматическую паузу включаем приемник. Это делается, с целью чтобы приемник до того, как окажется в надежных руках передатчика не наелся помех.

Настраиваем и включаем DMA приемника и передатчика. Бит CHEN остается в нуле, т.к. нас сейчас интересует однократный прием/передача. Первые 18 битов регистра DP (xr3) так же оставляем нулевыми, так как указатель на следующую цепочку нам сейчас не нужен.

Далее останавливаемся в бесконечном цикле

Теперь посмотрим насколько все работает, запустив отладчик.

В массиве передачи лежат данные.

Массив, в который мы передаем изначально пуст

Когда же мы доходим до пустых операторов то там появляются передаваемые данные

Как видно передача произошла корректно. В следующий раз рассмотрим передачу по LVDS между процессорами, благо на отладочной плате у меня их два. А на этом закончу, спасибо за внимание.

![Lvds что это в ноутбуке. tft 18[1]. Lvds что это в ноутбуке фото. Lvds что это в ноутбуке-tft 18[1]. картинка Lvds что это в ноутбуке. картинка tft 18[1]. Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компанией Texas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин. Lvds что это в ноутбуке. tft 18[1]. Lvds что это в ноутбуке фото. Lvds что это в ноутбуке-tft 18[1]. картинка Lvds что это в ноутбуке. картинка tft 18[1]. Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компанией Texas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин.](https://mk42.ru/images/tft_18[1].png)

![Lvds что это в ноутбуке. tft 19[1]. Lvds что это в ноутбуке фото. Lvds что это в ноутбуке-tft 19[1]. картинка Lvds что это в ноутбуке. картинка tft 19[1]. Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компанией Texas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин. Lvds что это в ноутбуке. tft 19[1]. Lvds что это в ноутбуке фото. Lvds что это в ноутбуке-tft 19[1]. картинка Lvds что это в ноутбуке. картинка tft 19[1]. Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компанией Texas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин.](https://mk42.ru/images/tft_19[1].png)

![Lvds что это в ноутбуке. tft 20[1]. Lvds что это в ноутбуке фото. Lvds что это в ноутбуке-tft 20[1]. картинка Lvds что это в ноутбуке. картинка tft 20[1]. Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компанией Texas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин. Lvds что это в ноутбуке. tft 20[1]. Lvds что это в ноутбуке фото. Lvds что это в ноутбуке-tft 20[1]. картинка Lvds что это в ноутбуке. картинка tft 20[1]. Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компанией Texas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин.](https://mk42.ru/images/tft_20[1].png)

![Lvds что это в ноутбуке. tft 22[1]. Lvds что это в ноутбуке фото. Lvds что это в ноутбуке-tft 22[1]. картинка Lvds что это в ноутбуке. картинка tft 22[1]. Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компанией Texas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин. Lvds что это в ноутбуке. tft 22[1]. Lvds что это в ноутбуке фото. Lvds что это в ноутбуке-tft 22[1]. картинка Lvds что это в ноутбуке. картинка tft 22[1]. Низковольтная дифференциальная передача сигналов (англ. low-voltage differential signaling или LVDS) — способ передачи электрических сигналов, позволяющий передавать информацию на высоких частотах при помощи дешёвых соединений на основе медной витой пары. Стандарт разрабатывался и продвигался компанией Texas Instruments. Начиная с 1994 года низковольтная дифференциальная передача сигналов используется в компьютерной индустрии, где нашла широкое применение для создания высокоскоростных компьютерных сетей и компьютерных шин.](https://mk42.ru/images/tft_22[1].png)